### **Chili2S Module Datasheet**

Rev. 0.7, October 2020

### **GENERAL DESCRIPTION**

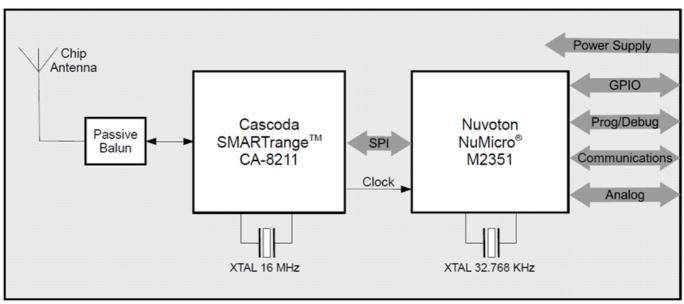

The Chili2S module is a fully-featured Thread-certified wireless module solution for IEEE 802.15.4 communications in the 2.4GHz band. It pairs the Cascoda CA-8211 SMARTRange™ transceiver and a Cortex®-M23 TrustZone® microcontroller.

With industry leading power consumption and sensitivity performance, it delivers unparalleled range without external amplifier components, thus providing whole-house connectivity in any market on the planet.

#### **FEATURES**

- SMARTRange™ CA-8211 IEEE 802.15.4 modem

- · Thread-certified component for every role

- Industry-leading receive sensitivity of -105dBm

- Programmable transmit power of -3dBm to +9dBm

- Industry-leading link budget of 114dB

- Integrated MAC low-power co-processor

- NuMicro® M2351 TrustZone® MCU

- Arm® Cortex®-M23 Architecture

- · Highly robust security for IoT applications

- 512 KB dual-bank application ROM (APROM) for Over-The-Air (OTA) upgrade

- 96 KB on-chip SRAM

- · Communication interfaces (UART, I2C, SPI, USB)

- · Analog Interfaces (ADC, DAC, Comp)

- Smart Card (ISO 7816) and SD Card Interfaces

- World-class energy consumption

- World's best receiver efficiency

14mA (42mW) at -105dBm sensitivity (0.0316nW)

Figure of Merit (FoM) 0.75 (mW\*nW)<sup>-1</sup>

- 19mA at +9dBm transmit power

- ∘ 3µA sleep mode

- Industrial temperature range: -40°C to +85°C

- Wide supply voltage range: 2.1V to 3.6V

- Chip antenna and all other RF components integrated on module

- 16 MHz crystal for system clock and 32.768 kHz crystal for low-power RTC functionality

- Module size: 27.00 x 21.05 mm

#### DEVELOPMENT TOOLS

• Certified Thread stack based on OpenThread

- Optimised interface for the M2351 MCU and the CA8211 hardware MAC

- Module can be detached node running the network stack and application or coprocessor for hosts running Linux within a Thread mesh network

- · Cascoda SDK, making full use of CMake as a build system

- · Code available open-source on GitHub

#### BENEFITS

**Equipment cost:** Increased range removes the need for external power amplifiers, thereby reducing component BOM.

**Installation cost:** Greater datalink reliability lessens the need for skilled installers, and the consumer can self-install.

**Maintenance cost:** Lower power consumption means that batteries last longer, thereby minimising maintenance cost.

**Development time**: Use of pre-certified module minimises product development time.

#### **APPLICATIONS**

- Home and building automation

- Consumer electronics

- · Lighting systems

- Heating, ventilation & air-conditioning systems (HVAC)

- Smart grid (AMI/AMR)

- Asset tracking (active RFID)

- Industrial control and monitoring

- · Assisted living & telecare

| Table of Contents                                     |    |

|-------------------------------------------------------|----|

| 1 Overview.                                           | 3  |

| 2 Hardware Description                                | 4  |

| 2.1 Module Pin Configuration.                         |    |

| 2.2 Recommended Footprint                             | 5  |

| 2.3 Pin Descriptions.                                 | 6  |

| 2.4 Multi-Function Pin (MFP) Mapping                  | 7  |

| 2.5 JTAG/SWD ICE Connector for Programming and Debug. | 8  |

| 2.6 <u>Unique Device ID</u>                           | 8  |

| 2.7 Power Supply                                      |    |

| 2.8 RF Circuitry                                      |    |

| 3 Electrical Specification.                           |    |

| 3.1 Absolute Maximum Ratings                          |    |

| 3.2 Environmental Conditions.                         | 9  |

| 3.3 Recommended Operating Conditions.                 | 9  |

| 3.4 <u>Digital Pin Characteristics</u>                | 9  |

| 3.5 Supply Currents.                                  |    |

| 3.6 General RF Characteristics                        |    |

| 3.7 Receiver RF Characteristics.                      |    |

| 3.8 <u>Transmitter RF Characteristics</u> .           |    |

| 4 Software Support                                    |    |

| 5 Regulatory Approvals                                | 12 |

| 5.1 Approved Antenna                                  | 12 |

| 5.2 <u>US (FCC)</u>                                   | 12 |

| 5.3 <u>Canada (IC)</u>                                |    |

| 5.4 Europe (CE)                                       |    |

| 6 Soldering Information                               | 14 |

| 7 References.                                         | 14 |

| 8 Revision History                                    | 14 |

### 1 Overview

The Chili2S module is a highly-integrated module for developing Thread® / IEEE 802.15.4 low-power wireless personal area network (WPAN) applications. It combines the Nuvoton M2351 Cortex®-M23 TrustZone® microcontroller with the Cascoda CA-8211 Thread® certified 2.4 GHz IEEE 802.15.4 transceiver modem. The main features of the Chili2S module are:

- Nuvoton M2351 Arm® Cortex®-M23 TrustZone® MCU

- Arm® TrustZone® technology

- 512k bytes of Flash Application ROM (APROM) memory, dual bank for Over-The-Air (OTA) upgrade

- 96k bytes of SRAM

- Up to 64MHz core frequency

- Cascoda SMARTRange™ CA-8211 IEEE 802.15.4 2.4 GHz transceiver modem

- Thread<sup>®</sup> certified component for every role

- Industry-leading link budget of 114 dB

- -105 dBm receiver sensitivity

- Up to 9dBm transmit power

- 19mA transmit current consumption at 9dBm

- 14mA receive current consumption

- 200nA low-power mode

- Module sleep current as low as 3uA

- 16MHz crystal oscillator supplying the system clock for both radio and MCU

- 32.768 kHz crystal oscillator for low-power RTC functionality

- · Pin access via edge pads to

- Up to 14 digital GPIOs with mappable Multi-Function Pin (MFP) functionality

- Communication interfaces (UART, I2C, SPI, USB)

- Analog Interfaces (ADC, DAC, comparator)

- · SMD chip antenna

Figure 1.1: Chili2S Block Diagram

# 2 Hardware Description

# 2.1 Module Pin Configuration

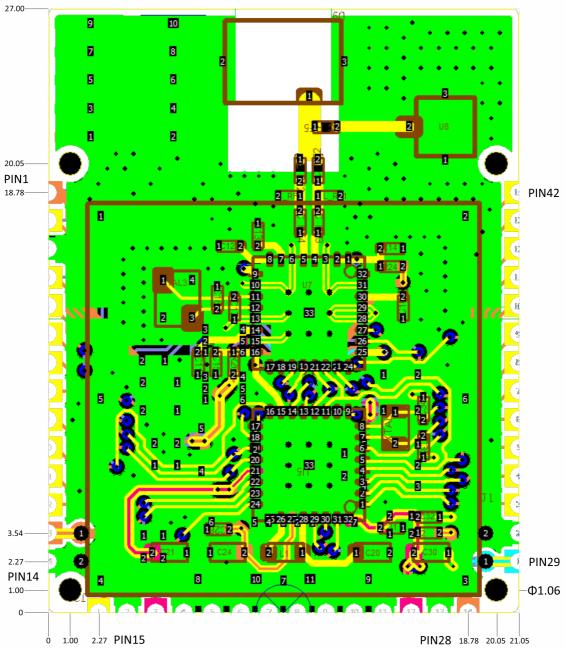

The following figure shows the front view of the Chili2S module. The edge pads (Pin1 to Pin42) for solder-down are on 1.27mm pitch.

Figure 2.1: Chili2S Module Front View (Unit:mm)

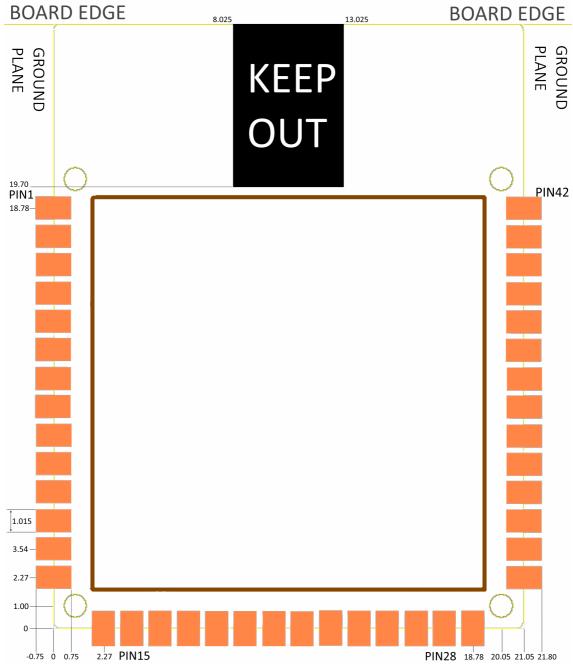

# 2.2 Recommended Footprint

Figure 2.2: Chili2S Module Recommended Footprint (Unit:mm)

# 2.3 Pin Descriptions

| Pin | Name                | Туре       | M2351 Port | Description                                   |

|-----|---------------------|------------|------------|-----------------------------------------------|

| 1   | VDD33               | Supply     | -          | 3.3V Power Supply                             |

| 2   | TMS                 | GPIO       | PF.0       | ICE/JLINK Data                                |

| 3   | GND                 | Ground     | -          | Module Ground                                 |

| 4   | тск                 | GPIO       | PF.1       | ICE/JLINK Clock                               |

| 5   | PB.12               | GPIO       | PB.12      | General Purpose Digital I/O                   |

| 6   | PB.13               | GPIO       | PB.13      | General Purpose Digital I/O                   |

| 7   | -                   | GPIO       | PB.14      | NC <sup>1)</sup>                              |

| 8   | -                   | GPIO       | PC.1       | NC¹)                                          |

| 9   | -                   | GPIO       | PC.0       | NC¹)                                          |

| 10  | TRSTX <sup>3)</sup> | Digital In | -          | System Reset and ICE/JLINK Reset (active low) |

| 11  | PA.13               | GPIO       | PA.13      | General Purpose Digital I/O                   |

| 12  | PA.14               | GPIO       | PA.14      | General Purpose Digital I/O                   |

| 13  | VDD33               | Supply     | -          | 3.3V Power Supply                             |

| 14  | GND                 | Ground     | -          | Module Ground                                 |

| 15  | PA.15               | GPIO       | PA.15      | General Purpose Digital I/O                   |

| 16  | GND                 | Ground     | -          | Module Ground                                 |

| 17  | PA.12               | GPIO       | PA.12      | General Purpose Digital I/O                   |

| 18  | GND                 | Ground     | -          | Module Ground                                 |

| 19  | GND                 | Ground     | -          | Module Ground                                 |

| 20  | GND                 | Ground     | -          | Module Ground                                 |

| 21  | GND                 | Ground     | -          | Module Ground                                 |

| 22  | GND                 | Ground     | -          | Module Ground                                 |

| 23  | GND                 | Ground     | -          | Module Ground                                 |

| 24  | GND                 | Ground     | -          | Module Ground                                 |

| 25  | GND                 | Ground     | -          | Module Ground                                 |

| 26  | AVDD33              | Supply     | -          | Filtered 3.3V Supply <sup>2)</sup>            |

| 27  | GND                 | Ground     | -          | Module Ground                                 |

| 28  | VDD33               | Supply     | -          | 3.3V Power Supply                             |

| 29  | -                   | -          | -          | NC¹)                                          |

| 30  | GND                 | Ground     | -          | Module Ground                                 |

| 31  | PB.5                | GPIO       | PB.5       | General Purpose Digital I/O                   |

| 32  | PB.4                | GPIO       | PB.4       | General Purpose Digital I/O                   |

| 33  | PB.3                | GPIO       | PB.3       | General Purpose Digital I/O                   |

| 34  | PB.2                | GPIO       | PB.2       | General Purpose Digital I/O                   |

| 35  | PB.1                | GPIO       | PB.1       | General Purpose Digital I/O                   |

| 36  | PB.0                | GPIO       | PB.0       | General Purpose Digital I/O                   |

| 37  | -                   | GPIO       | PF.5       | NC¹)                                          |

| 38  | -                   | GPIO       | PF.4       | NC¹)                                          |

| 39  | -                   | GPIO       | PA.3       | NC¹)                                          |

| 40  | -                   | GPIO       | PA.0       | NC¹)                                          |

| 41  | -                   | GPIO       | PA.2       | NC¹)                                          |

| 42  | -                   | GPIO       | PA.1       | NC¹)                                          |

**Table 2.1: Chili2S Module Pin Descriptions**

#### Notes:

- 1) NC: Do not connect, as pin is internally connected on module.

- 2) AVDD33 is a filtered supply output generated by the module for noise-sensitive peripherals. Do not connect to VDD33.

- 3) TRSTX (Pin 10) can be used by an external host to reset the Chili2S module. Leave unconnected if not used.

### 2.4 Multi-Function Pin (MFP) Mapping

The GPIO pins on the module can be assigned to specific functions including analog interfaces, communications interfaces and digital functionality. The table below summarises the MFP functions for all GPIO pins accessible on the module. For further information refer to the Nuvoton M2351 Technical Reference Manual [4].

| Pin | GPIO  | Default       |               | Analog      |                           | Co                         | mmuni       | cations      | Interfac           | се          |              |                   | D           | igital                     |               |            |

|-----|-------|---------------|---------------|-------------|---------------------------|----------------------------|-------------|--------------|--------------------|-------------|--------------|-------------------|-------------|----------------------------|---------------|------------|

|     | Port  | Function      | ADC           | DAC         | COMP                      | UART                       | I2C         | SPI          | USB                | CAN         | I2S          | Sma<br>rt<br>Card | SD<br>Card  | PWM                        | QEI           | Tim<br>er  |

| 2   | PF.0  | ICE<br>TMS    | -             | -           | -                         | UART1<br>TXD               | I2C1<br>SCL | -            | -                  | -           | -            | -                 | -           | BPWM1<br>CH0               | -             | -          |

| 4   | PF.1  | ICE<br>TCK    | -             | -           | -                         | UART1<br>RXD               | I2C1<br>SDA | -            | -                  | -           | -            | -                 | -           | BPWM1<br>CH1               | -             | -          |

| 5   | PB.12 | UART0<br>RXD  | EADC0<br>CH12 | DAC0<br>OUT | ACMP0<br>P2 <sup>3)</sup> | UART0<br>RXD               | I2C2<br>SDA | -            | -                  | -           | -            | -                 | SD0<br>nCD  | EPWM1<br>CH3               | -             | TM3<br>EXT |

| 6   | PB.13 | UART0<br>TXD  | EADC0<br>CH13 | DAC1<br>OUT | ACMP0<br>P3 <sup>4)</sup> | UART0<br>TXD               | I2C2<br>SCL | -            | -                  | -           | -            | -                 | -           | EPWM1<br>CH2               | -             | TM2<br>EXT |

| 11  | PA.13 | GPIO<br>PA.13 | -             | -           | -                         | UART4<br>RXD               | I2C1<br>SDA | SPI2<br>CLK  | D-                 | CAN0<br>RXD | I2S0<br>MCLK | SC2<br>RST        | -           | BPWM1<br>CH3               | QEI1<br>A     | -          |

| 12  | PA.14 | GPIO<br>PA.14 | 1             | 1           | -                         | UART0<br>TXD               | I2C2<br>SCL | SPI2<br>MISO | D+                 | 1           | I2S0<br>DI   | SC2<br>DAT        | -           | BPWM1<br>CH4               | QEI1<br>B     | -          |

| 15  | PA.15 | GPIO<br>PA.15 | -             | -           | -                         | UART0<br>RXD               | I2C2<br>SDA | SPI2<br>MOSI | OTG<br>ID          | 1           | I2S0<br>DO   | SC2<br>CLK        | -           | BPWM1<br>CH5 <sup>5)</sup> | -             | -          |

| 17  | PA.12 | GPIO<br>PA.12 | 1             | 1           | -                         | UART4<br>TXD               | I2C1<br>SCL | SPI2<br>SS   | VBUS <sup>8)</sup> | CAN0<br>TXD | I2S0<br>BCLK | SC2<br>PWR        | -           | BPWM1<br>CH2               | QEI1<br>INDEX | -          |

| 31  | PB.5  | GPIO<br>PB.5  | EADC0<br>CH5  | 1           | ACMP1<br>N                | UART5<br>TXD               | I2C0<br>SCL | SPI1<br>MISO | -                  | ı           | I2S0<br>BCLK | SC0<br>CLK        | SD0<br>DAT3 | EPWM0<br>CH0               | 1             | TM0        |

| 32  | PB.4  | GPIO<br>PB.4  | EADC0<br>CH4  | 1           | ACMP1<br>P1               | UART5<br>RXD               | I2C0<br>SDA | SPI1<br>MOSI | -                  | 1           | I2S0<br>MCLK | SC0<br>DAT        | SD0<br>DAT2 | EPWM0<br>CH1               | i             | TM1        |

| 33  | PB.3  | GPIO<br>PB.3  | EADC0<br>CH3  | -           | ACMP0<br>N                | UART1<br>TXD <sup>1)</sup> | -           | SPI1<br>CLK  | -                  | -           | I2S0<br>DI   | SC0<br>RST        | SD0<br>DAT1 | EPWM0<br>CH2               | -             | TM2        |

| 34  | PB.2  | GPIO<br>PB.2  | EADC0<br>CH2  | -           | ACMP0<br>P1               | UART1<br>RXD <sup>2)</sup> | -           | SPI1<br>SS   | -                  | -           | I2S0<br>DO   | SC0<br>PWR        | SD0<br>DAT0 | EPWM0<br>CH3               | -             | ТМ3        |

| 35  | PB.1  | GPIO<br>PB.1  | EADC0<br>CH1  | -           | -                         | UART2<br>TXD               | I2C1<br>SCL | -            | -                  | -           | I2S0<br>LRCK | -                 | SD0<br>CLK  | EPWM0<br>CH4 <sup>6)</sup> | -             | -          |

| 36  | PB.0  | GPIO<br>PB.0  | EADC0<br>CH0  | -           | -                         | UART2<br>RXD               | I2C1<br>SDA | -            | -                  | -           | -            | -                 | SD0<br>CMD  | EPWM0<br>CH5 <sup>7)</sup> | -             | -          |

Table 2.2: Multi-Function Pin (MFP) Functionality for the Chili2S GPIO Pins

#### Notes:

- 1) Also programmable as UART5 nRTS

- 2) Also programmable as UART5\_nCTS

- 3) Also programmable as ACMP1\_P2

- 4) Also programmable as ACMP1\_P3

- 5) Also programmable as EPWM\_SYNC\_IN

- 6) Also programmable as EPWM1\_CH4 or EPWM0\_BRAKE0

- 7) Also programmable as EPWM1\_CH5 or EPWM0\_BRAKE1

- 8) If pin 17 (PA.12) is used as USB VBUS, note that this is a standard 3.3V I/O pin and should **not** be connected to 5V. Two diodes should be connected in series for a 1.5V voltage drop to safely connect VBUS from a USB host to pin 17.

### 2.5 JTAG/SWD ICE Connector for Programming and Debug

A footprint is supplied on the bottom side of the module for a 10-pin connector to directly connect a programmer or debugging interface, for example a Segger J-Link Debug Probe.

| TRSTX | 10 | 9 | GND   |

|-------|----|---|-------|

| NC    | 8  | 7 | GND   |

| NC    | 6  | 5 | GND   |

| TCK   | 4  | 3 | GND   |

| TMS   | 2  | 1 | VDD33 |

Figure 2.3: 10-Pin Header for JTAG/ICE Programming and Debug

Note that the Pinout in Figure 2.3 shows the module bottom side view and is therefore mirrored compared to the footprint indication on the top left of Figure 2.1.

Note that all JTAG/SWD signals can also be accessed via the edge pads of the module.

#### 2.6 Unique Device ID

Each CHILI2 module is programmed with a unique and non-erasable 64-bit device identification code which can be read by software and used for addressing and other identification purposes.

### 2.7 Power Supply

All VDD33 pins (pins 1, 13 and 28) are connected to the same net on the module, therefore only one connection is required to supply the module. It is however recommended to connect as many as VDD33 pins as possible to decrease impedance for the power connections. No additional external components such as supply filters are required.

AVDD33 is a filtered version of VDD33 used both on the module and connected to pin 26 as analog power output, so it can be used to supply noise-sensitive off-module peripherals. It should **not** be connected to VDD33.

### 2.8 RF Circuitry

The Chili2S module uses a passive balun design for impedance matching and converting the differential signal of the CA-8211 to a single-ended  $50\Omega$  signal for connecting the SMD chip antenna.

When mounting the Chili2S module onto a host board, the module top edge should be aligned with the board edge with the antenna facing out, see Figure 2.2. To maximise range, an adequate ground plane must be provided on the host PCB. Correctly positioned, the ground plane on the host PCB will contribute significantly to the antenna performance. The area around and under the antenna, marked KEEP OUT, must be kept clear of conductors or other metal objects on any layer of the host board.

### 3 Electrical Specification

This section specifies important parameters for the Chili2S module. For more detailed information refer to the Nuvoton M2351 Datasheet [3] and the Cascoda CA-8211 Datasheet [2].

## 3.1 Absolute Maximum Ratings

| Parameter                 | Conditions | Min  | Тур | Max | Units |

|---------------------------|------------|------|-----|-----|-------|

| Voltage (on any pin)      |            | -0.3 | -   | 3.9 | V     |

| Storage Temperature Range |            | -65  | -   | 150 | °C    |

| Input RF Level            |            | -    | -   | +10 | dBm   |

### **Table 3.1: Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the module. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 3.2 Environmental Conditions

| Parameter | Conditions                         | Min  | Тур | Max  | Units |

|-----------|------------------------------------|------|-----|------|-------|

| ESD       | Human-body model, JEDEC STD 22     | -    | -   | 2000 | V     |

|           | Charged-device model, JEDEC STD 22 | -    | -   | 500  | V     |

| MSL       |                                    | MSL3 |     |      |       |

**Table 3.2: Environmental Conditions**

### 3.3 Recommended Operating Conditions

| Parameter                                        | Min | Тур | Max | Units |

|--------------------------------------------------|-----|-----|-----|-------|

| Operating Supply Voltage – Device Supply (VDD33) | 2.1 | -   | 3.6 | V     |

| Operating Temperature                            | -40 | -   | 85  | °C    |

**Table 3.3: Recommended Operating Conditions**

### 3.4 Digital Pin Characteristics

| Parameter                                    | Symbol          | Conditions                 | Min   | Тур | Max  | Units |

|----------------------------------------------|-----------------|----------------------------|-------|-----|------|-------|

| Input Low Voltage (TTL Input)                | V <sub>IL</sub> | VDD33=3.3V                 | -     | -   | 0.8  | V     |

| Input High Voltage (TTL Input)               | V <sub>IH</sub> | VDD33=3.3V                 | 2.0   | -   | -    | V     |

| Pull-up Resistor                             | R <sub>PU</sub> |                            | -     | 53  | -    | kΩ    |

| Input Leakage Current @ V <sub>i</sub> =3.3V | I <sub>1</sub>  |                            | -     | -   | 1    | uA    |

| Output Sink Current                          | I <sub>OL</sub> | VDD33=3.3V, Vin=VSS+0.4V   | 3.6   | -   | 19.9 | mA    |

| Output Source Current                        | I <sub>OH</sub> | VDD33=3.3V, Vin=VDD33-0.4V | -20.6 | -   | -3.4 | mA    |

**Table 3.4: Digital Pin Characteristics**

### 3.5 Supply Currents

Specified for VDD33=3.3V, T=25'C, System Clock=16MHz.

| Parameter                   | Symbol                | Conditions                        | Min | Тур      | Max | Units    |

|-----------------------------|-----------------------|-----------------------------------|-----|----------|-----|----------|

| Transmit                    | IDD <sub>Tx</sub>     | Tx Power +9 dBm<br>Tx Power 0 dBm |     | 20<br>13 |     | mA<br>mA |

| Receive                     | IDD <sub>Rx</sub>     | -105 dBm Sensitivity              |     | 15       |     | mA       |

| Processor active, Radio Off | IDD <sub>ACTIVE</sub> |                                   |     | 1.5      |     | mA       |

| Sleep Mode                  | IDD <sub>SLEEP</sub>  |                                   |     | 3        |     | uA       |

**Table 3.5: Supply Currents**

# 3.6 General RF Characteristics

| Parameter             | Symbol          | Conditions          | Min  | Тур | Max  | Units  |

|-----------------------|-----------------|---------------------|------|-----|------|--------|

| Frequency Range       | I <sub>FR</sub> | As specified by [1] | 2405 |     | 2480 | MHz    |

| Number of Channels    |                 | As specified by [1] |      | 16  |      |        |

| Data Rate             | DR              | As specified by [1] |      | 250 |      | kbit/s |

| TX/RX Turnaround Time |                 | As specified by [1] |      |     | 192  | μs     |

**Table 3.6: General RF Characteristics**

### 3.7 Receiver RF Characteristics

| Parameter                        | Symbol | Conditions                          | Min | Тур        | Max | Units      |

|----------------------------------|--------|-------------------------------------|-----|------------|-----|------------|

| Receiver Sensitivity             |        | 1% PER, PSDU 20 bytes               |     | -105       |     | dBm        |

| Maximum Receiver Input Level     |        | 1% PER, PSDU 20 bytes               |     | 0          |     | dBm        |

| Symbol Rate Tolerance            |        |                                     | -80 |            | 80  | ppm        |

| Adjacent Channel Rejection Low   |        | -5 MHz                              |     | 22         |     | dB         |

| Adjacent Channel Rejection High  |        | +5 MHz                              |     | 35         |     | dB         |

| Alternate Channel Rejection Low  |        | -10 MHz                             |     | 50         |     | dB         |

| Alternate Channel Rejection High |        | +10 MHz                             |     | 50         |     | dB         |

| Spurious Emissions               |        | 30 MHz – 1 GHz<br>1 GHz – 12.75 GHz |     | -77<br>-52 |     | dBm<br>dBm |

| ED Range                         |        |                                     |     | 83         |     | dB         |

| ED Low Range Limit               |        |                                     |     | -104       |     | dBm        |

| ED High Range Limit              |        |                                     |     | -21        |     | dBm        |

| ED Accuracy within Range         |        |                                     |     | ±2         |     | dB         |

| ED LSB Value                     |        |                                     |     | 0.5        |     | dB         |

**Table 3.7: Receiver RF Characteristics**

# 3.8 Transmitter RF Characteristics

| Parameter                                                                     | Symbol | Conditions                                                      | Min | Тур                      | Max | Units |

|-------------------------------------------------------------------------------|--------|-----------------------------------------------------------------|-----|--------------------------|-----|-------|

| Output Power                                                                  |        |                                                                 | 0   |                          | 9   | dBm   |

| Transmitter EVM                                                               |        |                                                                 |     | 5                        | 10  | %     |

| Transmitter Harmonics<br>2 <sup>nd</sup> Harmonic<br>3 <sup>rd</sup> Harmonic |        | @9dBm transmit power                                            |     | -52<br>-74               |     | dBm   |

| Transmitter Spurious Emissions                                                |        | 30 – ≤1000MHz<br>>1 – 12.75GHz<br>1.8 – 1.9GHz<br>5.15 – 5.3GHz |     | -77<br>-50<br>-68<br>-67 |     | dBm   |

| Absolute PSD Limit                                                            |        | F-Fc >3.5MHz                                                    |     | -43                      |     | dBm   |

| Relative PSD Limit                                                            |        | F-Fc >3.5MHz                                                    |     | -35                      |     | dB    |

**Table 3.8: Transmitter RF Characteristics**

# **4 Software Support**

The Cascoda open-source Software Development Kit (SDK) is available on GitHub (<a href="https://github.com/Cascoda/cascoda-sdk">https://github.com/Cascoda/cascoda-sdk</a>) and contains the API, drivers and interfaces required for developing applications using OpenThread or custom IEEE 802-15-4 based network connectivity.

The Cascoda SDK kit for the Chili2S module and the Nuvoton M2351 MCU contains:

- Optimised and exhaustively tested MAC-level (MCPS/MLME) API and interface drivers

- Hardware-MAC interface and configuration for OpenThread, an open-source implementation of the Thread® IPv6 based wireless mesh networking stack (https://openthread.io/)

- Example library for sensor interface drivers

- Low power modes

- Examples for custom IEEE 802.15.4 MAC based applications

- Hardware abstraction functions for module I/O handling, timers etc.

#### **Build Environment**

The Cascoda SDK makes full use of CMake as a build system, to enable advanced configuration and cross-platform development in combination with the ARM® GCC compiler toolchain. Build environments for other embedded compilers (IAR, Keil) are also available.

# **5 Regulatory Approvals**

### 5.1 Approved Antenna

This device has been approved with an onboard chip antenna with 1.75 dBi gain for the specific board layout. Any antenna of the same type, with similar in-band and out-of-band characteristics and with the same or less gain, can be used without reassessment. In case of using an antenna of a different type and/or higher gain, reassessment and notification to the particular certification authority is required.

### 5.2 US (FCC)

#### **Compliance Statement**

The Chili2D module complies with part 15 of the FCC rules. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference, and

- 2. This device must accept any interference received, including interference that may cause undesired operation.

### **Radiation Exposure Statement**

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. This transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter. The end equipment should be installed and operated with a minimum distance of 20 centimeters between the radiator and your body.

#### Modular Approval

The Chili2D module meets the requirements for modular transmitter approval as detailed in the FCC public notice DA 00-1407.

It should be noted that:

"While the applicant for a device into which an authorized module is installed is not required to obtain a new authorization for the module, this does not preclude the possibility that some other form of authorization or testing may be required for the device (e.g., a WLAN into which an authorized module is installed must still be authorized as a PC peripheral, subject to the appropriate equipment authorization)."

-- FCC Public Notice DA 00-1407

Caution:

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

Usage of Channel 26 at full power will result in non-compliance to FCC standards. The Power setting for Channel 26 has been limited to a maximum of +4 dBm by software when using the Cascoda SDK, or, if the Cascoda SDK is not used, use Channel 26 with a reduced power setting of +4 dBm. For further details, please contact Cascoda.

#### Labeling Requirements

The user of this device is responsible for meeting the FCC labeling requirements. A clearly visible label on the exterior enclosure of an incorporating device must list the FCC ID "2ATTO-CHILI2" and the FCC notice above.

The exterior label should use the wording "Contains" or "Contains Transmitter Module". For example:

#### Contains FCC ID: 2ATTO-CHILI2

or

### **Contains Transmitter Module FCC ID: 2ATTO-CHILI2**

Any similar wording that expresses the same meaning may be used.

The OEM integrator must not provide information to the end user regarding how to install or remove this RF module or change RF related parameters in the user manual of the end product.

This device complies with Part 15.247 of FCC Rules.

This modular transmitter is only FCC authorized for the specific rule parts listed on the grant, and the host product manufacturer is responsible for compliance to any other FCC rules that apply to the host not covered by the modular transmitter grant of certification.

If the grantee markets their product as being Part 15 Subpart B compliant (when it also contains unintentional-radiator digital circuity), then the grantee shall provide a notice stating that the final host product still requires Part 15 Subpart B compliance testing with the modular transmitter installed.

The following text shall be made available to the host product end user:

- · This device complies with Part 15 of FCC Rules, Operation is Subject to following two conditions:

- 1. This device may not cause harmful interference, and

- 2. This device must accept any interference received including interference that cause undesired operation.

Other than a product that is so small, or for such use that it is impracticable to label with a font size that is four-points or larger, the text should be placed on the host product.

#### Also for RF Exposure:

Co-location of this module with other transmitter that operate simultaneously are required to be evaluated using the FCC multi-transmitter procedures.

If the host manufacturer uses the module in a Mobile configuration then the following text is placed in the host product, user guide:

• This device complies with FCC RF radiation exposure limits set forth for an uncontrolled environment and must be installed to so that a separation distance of at least 20cm from all persons.

If the RF exposure conditions are different after module integration into a host product (eg: Portable usage, or co-location with another transmitter/ antenna), the this text must be altered as appropriate.

### 5.3 Canada (IC)

#### **Compliance Statement**

This Device complies with Industry Canada License-exempt RSS standard(s). Operation is subject to the following two conditions:

- 1. This device may not cause interference, and

- 2. This device must accept any interference, including interference that may cause undesired operation of the device.

The equipment complies with RF exposure limits set forth for an uncontrolled environment. The antenna(s) used for this transmitter must not be co-located or operating in conjunction with any other antenna or transmitter.

To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that permitted for successful communication.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes:

- 1. L'appareil ne doit pas produire de brouillage, et

- 2. L'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

L'équipement est conforme aux limites d'exposition aux RF établies pour un incontrôlés environnement. L'antenne(s) utilisée pour ce transmetteur ne doit pas être co-localisés ou fonctionner en conjonction avec toute autre antenne ou transmetteur.

Pour réduire les risques de brouillage radioélectrique à l'intention des autres utilisateurs, le type d'antenne et son gain doivent être choisies de façon que la puissance isotrope rayonnée équivalente (e.i.r.p) ne dépasse pas celle admise pour une communication réussie.

The end equipment should be installed and operated with a minimum distance of 20 centimeters between the radiator and your body.

L'équipement final devrait être installé et utilisé avec une distance minimum de 20 centimètres entre le radiateur et votre corps.

Usage of Channel 26 at full power will result in non-compliance to IC standards. The Power setting for Channel 26 has been limited to a maximum of +4 dBm by software when using the Cascoda SDK, or, if the Cascoda SDK is not used, use Channel 26 with a reduced power setting of +4 dBm. For further details, please contact Cascoda.

### **Labeling Requirements**

This Module is labelled with its own IC ID. If the IC ID Certification Number is not visible while installed inside another device, then the device should display the label on it referring the enclosed module. In that case, the final end product must be labelled in a visible area with the following:

"Contains IC: 25180-CHILI2"

"HVIN: CHILI2D" or

"Contains Transmitter Module IC: 25180-CHILI2"

"HVIN: CHILI2D"

## 5.4 Europe (CE)

This device is conform to the provisions of the requirements of the Radio Equipment Directive (RED, Radio Equipment Directive 2014/53/EU):

- ETSI EN 300 328 V 2.1.1

- ETSI EN 301 489-1 V2.1.1

- ETSI EN 301 489-17 V3.1.1

Note that every application using the Chili2D module will still need to perform the radio EMC tests on the end product according to EN 301 489-17.

The manufacturer must maintain a copy of the Chili2D module documentation and ensure the final product does not exceed the specified power ratings, antenna specifications, and/or installation requirements as specified in the documentation. If any of these specifications are exceeded in the final product, a submission must be made to a notified body for compliance testing to all required standards.

#### **Labeling & User Information Requirements**

The label on the final products which contain a Chili2D module must follow CE marking requirements.

### **6 Soldering Information**

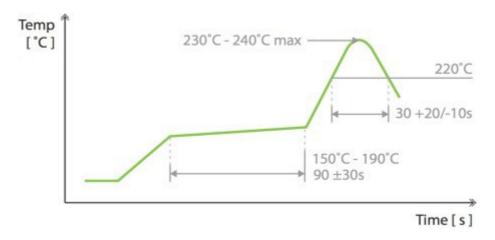

Figure 6.1: Soldering Temperature Time Profile for Reflow Soldering (Lead-Free Solder)

Cycles: it is recommended to do only one soldering cycle.

Cleaning: it's not recommended to clean the module. Solder paste residuals underneath the module cannot be removed.

### 7 References

- [1] IEEE Std 802.15.4™-2006: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (LR-WPANs)

- [2] Cascoda IEEE 802.15.4 Transceiver CA-8211 Datasheet, Rev. 1.0, January 2019, https://www.cascoda.com/wp-content/uploads/2019/01/CA-8211\_datasheet\_0119.pdf

- [3] Nuvoton NuMicro® Family M2351 Series Datasheet, Rev. 1.01, Feb 15, 2019, http://www.nuvoton.com/resource-files/DS\_M2351\_Series\_EN\_Rev1.01.pdf

- [4] Nuvoton NuMicro® Family M2351 Series Technical Reference Manual, Rev. 1.00, Aug, 2018, http://www.nuvoton.com/resource-files/TRM\_M2351\_Series\_EN\_Rev1.00.pdf

# **8 Revision History**

| Revision | Date         | Status | Comments                       |

|----------|--------------|--------|--------------------------------|

| 0.1      | 07 May 2019  |        | Pre-Release, for Review only.  |

| 0.2      | 30 May 2019  |        | Update image on the first page |

| 0.3      | 05 July 2019 |        | Update Image on the first page |

| 0.4      | 26 July 2019 |        | Update Chili2S Block Diagram   |

| 0.5      | 03 Sep 2019  |        | Preliminary Release            |

| 0.6      | 12 Sep 2019  |        | Added device ID                |